알테라, Quartus II 소프트웨어 버전 8.1 발표

“자신들의 차세대 시스템에 최신 초미세공정 FPGA 기술들을 적용하려는 기업들에게 디자인 시간과 엔지니어링 자원 관리의 중요성이 더욱 커지고 있다.”라고 시장조사기관인 가트너의 브라이언 루이스(Bryan Lewis) 수석 애널리스트는 말했다. 이어 그는, “FPGA의 공정이 갈수록 미세화되고 기능은 증가됨에 따라 디자인 팀이 생산성을 극대화하고 중대한 목표인 시장 진입 시기를 만족시킬 수 있도록 해주는 정교한 툴이 요구된다.”라고 덧붙였다.

한편, Acquisition Logic의 마이클 위릭(Michael Wyrick) 엔지니어링 부사장은, “우리의 고속 데이터 수집 보드를 사용하는 고객들은 실시간으로 데이터를 처리하는 솔루션을 더 빨리 공급받기를 원하고 있는데 이것이 바로 우리가 알테라의 FPGA 기술을 이용하는 이유이다.”라고 말했다. 그는 또, “우리 FPGA 기반 시스템들은 더욱 높은 성능과 더욱 낮은 전력을 요구하기 때문에 시장에 진입할 수 있는 창은 그만큼 좁아지고 있다. Quartus II 소프트웨어는 FPGA 디자인을 효율적으로 수행하기 위한 최상의 환경을 제공한다. 알테라의 디자인 소프트웨어를 사용하면 FPGA 개발에 드는 기간이 늘어나지 않으면서, 타이밍 최적화를 더 빨리 마치고, 소비전력 요건을 만족시키며 성능을 극대화할 수 있다.”라고 덧붙였다.

디자인 개발 더 빨라져

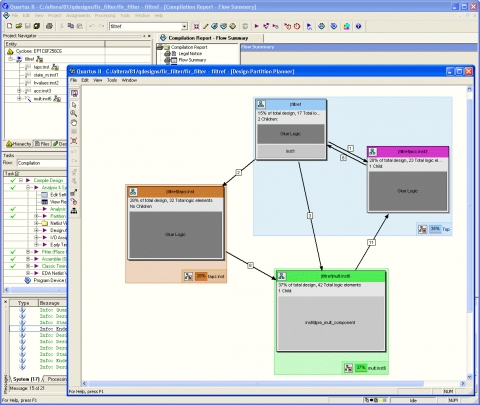

차세대 FPGA들의 기능이 더욱 커짐에 따라 제한된 개발 시간으로 인해 디자인 팀들에 대한 압박이 늘어난다. Quartus II 소프트웨어 버전 8.1은 전통적으로 시간이 많이 소요되는 작업들을 자동화함으로써 개발 속도를 높여준다. 디자인 파티션 플래너는 Quartus II 소프트웨어 버전 8.0에서 처음 도입되었는데, 버전 8.1에서는 자동화된 파티셔닝을 제공하여, 더 많은 디자이너들이 인크레멘탈 컴파일 (incremental compilation – 점증 컴파일)을 이용해 생산성을 향상시킬 수 있게 되었다. Quartus II 소프트웨어는 또한 과거 게이트로 구현되었던 클럭을 이에 상응하는 FPGA 아키텍처로 자동 변환함으로써 수동으로 클럭을 수정해야 했던 필요도 제거했다. 이러한 자동화된 기능들로 인해 디자인 팀들은 디자인에 부가가치를 구현하는 부분에 보다 많은 노력을 집중할 수 있게 되었다.

디자인 지원 확장돼

알테라는 지난 2008년 5월에 40 nm 공정의 Stratix IV FPGA를 발표함으로써 고성능, 고밀도 FPGA시장에서 리더쉽을 더욱 견고히 했다. 현재까지, 거의 600개에 달하는 고객사들이 알테라의 Stratix IV 얼리 어답터 프로그램에 참여해 이 중 많은 고객사들이 Quartus II 소프트웨어 버전 8.1을 이용해 다양한 시장의 다양한 애플리케이션을 위한 Stratix IV FPGA 디자인을 이미 시작했다. 버전 8.1은 Stratix IV의 핀 구성 및 저가형 제품들의 작동속도를 지원함으로써 고객들에 대한 지원을 한 단계 높였다. 이 소프트웨어는 8.5Gbps 트랜시버, 1.6Gbps LVDS 및 400MHz DDR 메모리에 대한 지원뿐 아니라 트랜시버 타이밍-모델에 대한 지원이 추가되었다. HardCopy ASIC 구현을 목표로 하는 디자이너를 위해 Quartus II 소프트웨어는 HardCopy IV ASIC용 초기 지원도 제공한다.

“알테라는 개발자의 생산성 향상을 선도하고 있다.”라고 알테라의 소프트웨어, 임베디드 및 DSP 수석 마케팅 이사인 크리스 발로우(Chris Balough)는 말했다. 또 그는 “Quartus II 소프트웨어 버전 8.1은 고밀도 FPGA 컴파일 시간이 타 회사의 솔루션들에 비해 3배 빠르도록 유지하는 알테라의 생산성 리더쉽 전통을 이어가고 있다”라고 덧붙였다.

Quartus II 소프트웨어 버전 8.1의 새로운 기능들

· SignalTap II 임베디드 로직 분석기 – 데이터 샘플링 컨트롤이 더욱 정교해져 디버깅 속도를 높이고 온칩 메모리 효율성을 향상시킨다.

· 강화된 SOPC 빌더 툴

o 새로운 HDL 템플릿으로 인해 SOPC 빌더를 이용해 IP를 재사용하는 작업의 속도가 빨라지고 간편해졌다.

o 새로운 Avalon 메모리 매핑 1/2 속도 브릿지로 인해 DDR SDRAM 액세스 지연이 훨씬 짧아졌다.

· 새로운 OS 지원 – 레드햇 엔터프라이즈 리눅스 5와 CentOS 4/5 (32 비트 및 64 비트) 지원

· 강화된 제3자 시뮬레이션 인터페이스 – 라이브러리 파일의 자동 컴파일을 지원해 시물레이션 구성이 더욱 빨라졌다.

· 새로운 Pin-Out 어드바이저 – pin-out 생성과 제3자의 보드 툴에 대한 인터페이스를 안내한다.

· Real Intent 검증 지원 – Real Intent 사의 Meridian FPGA Clock Domain Crossing (CDC) 소프트웨어는 사용하기 쉽고 자동화된 클럭 의도 검증을 제공하기 때문에 디자인 에러들을 잡아낼 수 있고 CDC 연산에 대한 신뢰를 갖게 해준다.

· 새롭고 강화된 IP 코어와 메가 기능들 – DSP, 메모리 및 프로토콜들이 개발을 가속화한다.

· 물리적인 통합 엔진 강화 – 이전 버전에 비해 평균 20퍼센트 짧은 시간 내에 타이밍이 중요한 블록들의 타이밍 디자인을 마칠 수 있다.

· 시놉시스 디자인 제약 (SDC) – SDC 템플릿들이 타이밍 제약 생성을 안내해 더 빨리 마칠 수 있도록 한다

Quartus II 소프트웨어에 대한 더욱 자세한 정보는 www.altera.com/quartus2에서 구할 수 있다.

가격과 구입 가능 시기

Quartus II 소프트웨어 버전 8.1의 정식 라이센스 버전(subscription edition)과 무료 웹 에디션은 모두 지금 다운로드 가능하다. https://www.altera.com/support/software/download/sof-download_center.html 또한 정식 라이센스 버전은 https://www.altera.com/literature/quartus2/q2acds-dvd.jsp 에서 DVD로 신청할 수도 있다. 알테라의 소프트웨어 라이센스 프로그램은 1년간 구독료에 소프트웨어 제품과 유지보수비를 통합함으로써 Altera 디자인 소프트웨어를 간편하게 구매할 수 있도록 만든다. 정식 라이센스 사용자는 Quartus II 소프트웨어의 ModelSim Altera 판과 알테라의 가장 인기 있는 (DSP와 메모리) IP 코어 11개를 포함하는 IP 베이스 스위트에 대한 풀 라이선스를 받는다. 연간 소프트웨어 라이센스료는 PC 1 대당 미화 2,495달러이며, 알테라의 eStore (http://www.altera.com/buy/buy-index.html)나 공인 딜러를 통해 구입 가능하다.

알테라에 대하여

알테라의 프로그래머블 솔루션은 시스템과 반도체 회사들이 관련 시장에서 빠르고 비용 효과적인 혁신과 차별화를 이루도록 한다. 보다 더 자세한 내용은 www.altera.com에서 구할 수 있다.

웹사이트: http://www.altera.com

연락처

홍보대행 SMC 조혜란 02-3445-3283