수볼타, 2011 국제전자소자학회(IEDM)에서 DDC(Deeply Depleted Channel) 트랜지스터 구조 기술 발표

- 전력 소모 감소 및 CMOS 스케일링에 혁신적인 소자 기술 적용

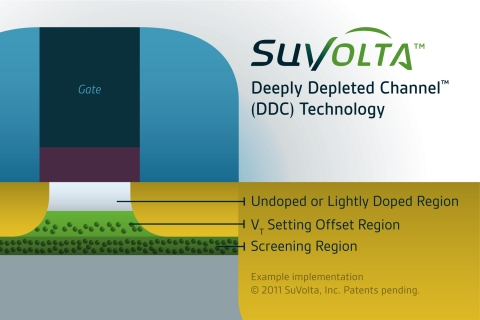

수볼타의 DDC (Deeply Depleted Channel) 트랜지스터 기술

수볼타의 DDC 트랜지스터는 문턱전압 (VT) 변화폭을 줄임으로써 지속적인 CMOS 스케일링을 가능하게 해 준다. 이 구조는 게이트(gate)에 전압이 가해졌을 때 깊게 공핍된 채널(Deeply Depleted Channel)의 형성을 통해 동작된다. DDC 채널의 전형적인 구조는 몇 가지 영역들, 즉, 도핑 되지 않았거나 혹은 매우 낮게 도핑 된 영역, 문턱전압 (VT) 셋팅 오프셋 영역, 스크리닝 영역으로 이루어져 있다. 수볼타의 DDC 트랜지스터 구조 구현 방식은 반도체 웨이퍼 팹 시설 및 특정한 칩 설계 요구 조건에 따라 달라질 수 있다.

도핑 되지 않았거나 혹은 매우 낮게 도핑 된 영역은 채널의 도펀트를 제거 함으로써 깊게 공핍된 채널을 이루게 한다. 이렇게 함으로써 랜덤 도펀트 변동(RDF)을 줄이고 VDD 스케일링을 가능하게 하며 모빌리티를 증가시켜서 유효전류를 크게 해준다.

문턱전압 (VT) 셋팅 오프셋 영역은 채널 모빌리티를 감소시키지 않으면서 트랜지스터의 문턱전압 레벨을 셋팅 할 수 있게 한다. 이 영역은 기존 트랜지스터 대비해 VT 변화폭이 적어지도록 개선해 준다.

스크리닝 영역은 전하를 제한시켜 공핍영역 깊이를 셋팅시키며, 필요에 따라 다이나믹 바디 바이어싱을 통해 VT 를 조절 할 수 있는 바디의 역할을 할 수 있게 해 준다.

DDC 트랜지스터는 공급 전원 전압을 낮춤으로써 저전력 동작을 가능하게 해 준다. 문턱전압 (VT) 변화폭을 줄임으로써, 수볼타의 DDC 기술을 적용한 칩에서는 다음과 같은 이점을 얻을 수 있다.

- 성능에 영향을 주지 않으면서 30% 이상의 공급전압 감소 실현

- 매우 적은 누수 전력

- 설계 시 고려할 오버 디자인 마진 축소 가능

- 수율 개선

또한, DDC 트랜지스터는 오늘날 저전력 제품 설계 시 반드시 필요한 멀티 VT 의 셋팅을 가능하게 해 준다. VT 변화폭의 상당한 감소에 의한 장점 외에도 DDC 트랜지스터는 고속 동작 및 저전력 동작을 가능하게 해 주는 다음과 같은 장점들이 있다.

- 증가된 채널 모빌리티에 따른 가동 전류 증대

- DIBL(Drain Induced Barrier Lowering) 감소

- 증가된 바디 계수(Body coefficient)를 이용한 트랜지스터 VT 컨트롤 범위 확대

수볼타의 최고기술책임자인 스콧 톰슨(Scott Thompson) 박사는 “칩을 작게 만드는 것 만으로는 더 이상 아무 의미가 없는 때가 있다. 트랜지스터당 가격의 감소가 정체 되어 감에 따라, 리소그래피 비용의 증가는 이제 무어의 법칙의 끝이 다가 오고 있음을 보여주고 있다. 오랫동안 지속될 것이라고 믿었던 28nm와 20nm 공정에서도 그러한 때가 다가오고 있다”며, “마이크로프로세서를 제외하고, 모바일 시장용 칩의 대부분은 가격과 저전력 소모에 프리미엄이 있다. 수볼타의 DDC 구조의 특징은 오늘날 널리 사용되고 있는 CMOS 공정과 팹 시설에 완전히 호환하여 생산 가능한 유일한 트랜지스터 기술이며, 이 기술을 통해 반도체 기업들은 수년에 걸쳐 개발한 레거시 회로 IP 블록을 보존하고 사용할 수 있다”고 말했다.

클라이너 퍼킨스 코필드 앤 바이어스(Kleiner Perkins Caufield & Byers) 투자회사의 빌 조이(Bill Joy)는 “모바일 전자기기 분야의 산업이 지속적으로 성장하기 위해서는 코어 기술이 끊임없이 발전해야 한다”며, “수볼타는 현재 반도체 업계의 가장 당면한 과제인 전력 소비 감소 문제를 해결하기 위해 기존의 평면 벌크 CMOS 공정 기술과 호환되는 혁신적인 기술을 개발했다”고 말했다.

참고 자료

수볼타의 DDC 구조에 대한 자료 및 동영상 보기: www.suvolta.com/cmos-power/

수볼타 기술 라이센싱에 관련된 정보: http://www.suvolta.com/sales-inquiry/

후지쯔 반도체와 수볼타의 공동 IEDM 논문 관련 기사: www.suvolta.com/newsroom/press-releases/iedm

트위터: @http://twitter.com/SuVoltaInc

수볼타 개요

수볼타(Suvolta)는 성능은 유지하면서 반도체칩의 전력 소모를 크게 절감하는 반도체 기술을 개발하고 라이선스한다. 실리콘밸리에 위치하고 있는 수볼타 팀은 세계적인 엔지니어들과 과학자들로 구성되어 있으며, 반도체 업계의 발전에 기여한 오랜 기술 개발과 혁신의 역사를 자랑한다. 회사는 대표적인 벤처 캐피털 기업인 KPCB (Kleiner Perkins Caufield & Byers), 오거스트 캐피털, NEA로부터 자금을 지원받고 있다. 보다 자세한 정보는 www.suvolta.com를 방문하면 된다.

웹사이트: http://www.suvolta.com

연락처

The Hoffman Agency Korea

이지현 대리

02-737-2944

이메일 보내기