아테리스, PIANO 2.0 자동 인터커넥트 타이밍 클로저 기술 발표

SoC 인터커넥트 IP RTL을 이용하여 SoC 납기를 단축하고 R&D 비용을 절감하며 전력, 성능, 면적을 최적화

초미세 반도체 공정 기술과 핀펫(FinFET) 트랜지스터 사용이 증가하면서 온칩 인터커넥트는 타이밍 클로저 이슈에서 가장 중요한 원인이 되고 있다. 이러한 이슈들은 대개 설계 공정의 후반부에 발견되기 때문에 개발 일정에 차질을 빚게 하거나 제품 출시를 지연시키곤 한다. 현재 설계팀들은 ECO(engineering change order) 공정을 통해 칩 넷리스트에 파이프라인 단을 수동으로 삽입함으로써 이러한 문제를 처리하고 있다.

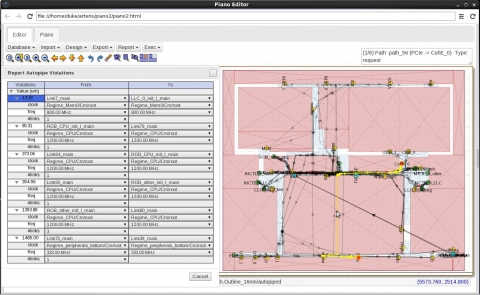

PIANO 2.0은 SoC 설계 플로우의 초반부터 작동하는 기술을 이용해 백엔드 타이밍 문제를 해결하기 때문에 일정 지연의 위험을 줄여준다. 이 새로운 기술은 아테리스의 FlexNoC 및 Ncore 인터커넥트 제품을 사용하는 고객들에게 물리적 인터커넥트 거리 개념을 알려준다. 우선, PIANO는 개별 인터커넥트 링크와 트레이스의 길이를 계산한 다음, 반도체 기술 공정에 대한 정보와 성능 목표를 활용하여 인터커넥트 파이프라인을 가까운 타이밍에 자동으로 연결한다. 그런 다음 PIANO는 시놉시스(Synopsis)나 케이던스(Cadence) 툴 체인의 물리적 합성 능력을 이용해 이 타이밍 클로저 회로에 대한 평가를 지원한다.

◇PIANO 2.0의 이점

-수동식 파이프라인 삽입 방식에 비해 타이밍 종료에 요구되는 시간을 줄임으로써 전반적인 일정 지연 위험을 완화. 잘 정의된 기법을 이용하여, 인터커넥트 타이밍 작업을 24시간 이내에 종료

-파이프라인 단을 과잉 공급하는 수동식 파이프라인 삽입 방식에 비해 인터커넥트 면적을 10~15% 감축

-파이프라인 로직 수가 적은 데다 LVT(low voltage threshold) 셀도 더 적게 사용하기 때문에 인터커넥트 전력 소비를 절감

-배치 및 배선(place and route, P&R) 툴이 더 좋은 시작점을 갖도록 하는 파이프라인 단 위치를 제공하기 때문에 비용 증가를 유발하는 P&R 반복을 제거

◇PIANO 2.0의 새로운 기능

-캐시 코히어런트 및 비-코히어런트 인터커넥트 서브시스템 모두에 자동화된 인터커넥트 타이밍 클로저 제공

-SoC 설계 개발 단계에서 타이밍 클로저 지침을 제공하기 위해 IP 목록으로부터 메타 플로어플랜(meta-floorplan) 생성

-제조 플로어플랜을 LEF/DEF 및 TCL 포맷으로 입력 및 출력

-다음과 같은 첨단 기능들을 갖춘 자동화된 파이프라인 삽입

개별 타이밍 경로들을 최적화하기 위한 타이밍 클로저 파라미터 편집

다중 주파수 및 전압 도메인 간의 교차를 자동으로 처리

타이밍 클로저 분석 보고서를 자동으로 생성

-시놉시스의 디자인 컴파일러 그래피컬 및 IC 컴파일러II(Synopsys’ Design Compiler Graphical and IC Compiler II)와 케이던스의 제너스 및 이노버스(Cadence’s Genus and Innovus) 물리적 합성 툴 체인 통합

아테리스의 찰스 자낙(K. Charles Janac) 회장 겸 CEO는 “PIANO 타이밍 클로저 패키지의 핵심 기술은 현재 생산 중인 몇몇 복잡한 핀펫 SoC 설계에 적용되고 있다”며 “PIANO 2.0은 아테리스의 Ncore 캐시 코히어런트 인터커넥트와 FlexNoC 비-코히어런트 인터커넥트 IP 제품 모두와 동작하는 차세대 자동 인터커넥트 타이밍 클로저 솔루션을 공급하기 위해 업계 선도적인 반도체 설계팀들과 18개월 동안 협력한 결과물”이라고 말했다.

PIANO 2.0 타이밍 클로저 패키지는 FlexNoC와 Ncore 인터커넥트 IP 라이선스에 추가하여 지금 즉시 활용이 가능하며, 추가적인 기능들은 2017년 2분기에 제공된다.

르네사스 일렉트로닉스 유럽 기술 센터 설계 서비스 담당(Manager, Design Services, European Technology Center, Renesas Electronics Europe) 홀스트 리저(Horst Rieger) 매니저는 “PIANO 2.0 자동 클로저 기술은 기존에 타이밍 클로저 이슈로 인해 발생하던 SoC 개발 일정 지연의 위험성을 낮춰준다. PIANO 2.0과 생성된 배치 가이드를 적용한 덕분에 르네사스는 복잡한 SoC 개발 일정을 당초 예상보다 앞당길 수 있었다”고 밝혔다.

시놉시스(Synopsys) CTO(Chief Technology Officer) 안툰 도믹(Dr. Antun Domic) 박사는 “핀펫 SoC 세대는 줄어든 드라이브 길이, 길어진 와이어 거리, 증가한 상대적 와이어 저항 및 높아진 성능 요건들로 인해 엄청난 타이밍 클로저 과제와 대면하고 있다. 아테리스의 PIANO 2.0 타이밍 클로저 솔루션과 시높시스의 디자인 컴파일러 그래피컬 및 IC 컴파일러 II 물리적 툴을 조합하면 설계 초기부터 최종 배치 및 배선 작업까지 인터커넥트 타이밍 클로저 공정을 향상시킬 수 있다. 우리는 SoC 인터커넥트 타이밍 클로저 공정을 자동화하기 위해 서로의 고객들과 협력해 나갈 수 있기를 기대한다”고 말했다.

린리 그룹(The Linley Group) 마이크 데믈러(Mike Demler) 수석 분석가는 “복잡한 핀펫 SoC에서 타이밍 종료는 SoC 설계자가 풀기 어려운 과제다. 아테리스의 새로운 PIANO 기술은 복잡한 SoC 인터커넥트에 대한 공정을 자동화하는 아테리스의 FlexNoC 물리적 타이밍 클로저 기술을 크게 향상시킨다”고 말했다.

Arteris 회사 개요

아테리스(Arteris, Inc.)는 다양한 애플리케이션 범위에 적합한 시스템온칩(SoC) 반도체를 신속하게 구현할 있는 시스템온칩 인터커넥트 IP(Systme-on-Chip interconnect IP)와 툴을 공급한다. 삼성, 화웨이(Huawei) / 하이실리콘(Hisilicon), 모빌아이(Mobileye), 알테라(Altera, 현 인텔), TI(Texas Instruments) 등 고객사의 반도체 설계자들이 급속도로 제품을 채택함에 따라 아테리스는 2012년, 2013년 2년 연속 500대 기업 및 딜로이트 선정 500대 고속 성장 기업(Deloitte Technology Fast 500 list) 리스트에 오른 유일한 반도체 IP 기업이다. 아테리스 제품 라인을 이용할 경우, 고객사들은 저전력, 고성능을 비롯해 더 효율적인 디자인 재사용 및 더 신속한 SoC 개발 이점을 누릴 수 있으며 개발 및 생산 단가를 획기적으로 절감할 수 있다. 상세 정보는 홈페이지를 참조하면 된다.

웹사이트: http://www.arteris.com

연락처

아테리스 홍보대행

페리엔

박윤희 실장

02-565-6625

이메일 보내기