어플라이드 머티어리얼즈, 옹스트롬 시대 칩 제조 위한 패터닝 솔루션 포트폴리오 확대

더 많은 스컬프타 패턴 형성 기술 활용 분야에서 모든 최첨단 로직 반도체 제조사와 협력

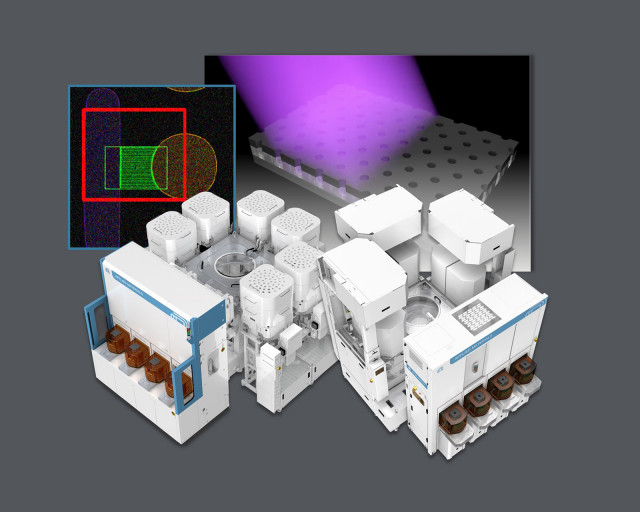

혁신적인 새로운 식각 시스템, CVD 패터닝 필름, 계측 솔루션 도입… EUV 및 하이 NA EUV 리소그래피 사용해 만든 칩 보완 및 개선

반도체 제조업체들은 2nm 이하 노드 공정으로 전환하면서 EUV 및 하이 NA EUV 패터닝 관련 에지 러프니스(roughness), 팁 간격(tip-to-tip spacing) 제한, 브릿지 결함, 에지 배치 오류 같은 문제를 해결하는데 새로운 재료 공학 및 계측 기술로부터 큰 도움을 받고 있다.

채택 증가 및 새로운 적용 분야 개발로 모멘텀 맞은 ‘스컬프타’

지난해 어플라이드는 반도체 제조사가 패턴 형태를 늘려 EUV 더블 패터닝 단계를 줄임으로써 싱글 EUV 또는 하이 NA EUV 노광에 비해 팁 간격을 더 좁힐 수 있는 ‘센튜라 스컬프타(Centura Sculpta)’ 패터닝 시스템을 발표했다. 어플라이드는 현재 모든 최첨단 로직 반도체 제조사와 협력하며 스컬프타 적용 분야를 넓히고 있다. 일례로, 팁 간격을 줄이는 것 외에도 반도체 제조사는 스컬프타를 이용해 브릿지 결함을 제거함으로써 패터닝 비용을 절감하고 칩 수율을 개선할 수 있다.

프라부 라자(Prabu Raja) 어플라이드 머티어리얼즈 반도체 사업부 사장은 “업계 선도 반도체 제조사들이 제조 공정에 스컬프타 시스템을 도입하고 EUV 더블 패터닝 단계 축소 외에도 응용 분야를 추가 모색하면서 좋은 성과를 거두고 있다”며 “스컬프타는 패터닝 엔지니어 툴킷에 편입된 완전히 새로운 도구다. 엔지니어들이 상상력을 발휘해 새로운 방식으로 어려운 문제를 해결하면서 더 많은 분야에 사용될 것”이라고 밝혔다.

라이언 러셀(Ryan Russell) 인텔 로직 기술 개발 그룹 부사장은 “패턴 형성은 인텔이 공정 기술 로드맵을 가속할 수 있는 혁신적인 해결책”이라며 “인텔은 옹스트롬 공정 노드를 위해 스컬프타 시스템을 도입한 후 처리량 개선, 웨이퍼 수율 향상, 공정 복잡성 감소, 비용 절감 등의 효과를 거뒀다. 패턴 형성은 새로운 첨단 패터닝 전략을 촉진하고, 리소그래피 프린트 경계를 확장하는 길을 연다”고 말했다.

박종철 삼성전자 파운드리 사업부 식각 기술팀 마스터는 “패터닝 형성 기술은 EUV 시대 주요 문제를 해결하는 혁신 기술”이라며 “삼성은 초기 개발 파트너로 4nm 공정에 대한 스컬프타 시스템을 평가하고 있다. 비용과 복잡성 감소, 수율 증가 같은 긍정적 결과를 기대한다”고 말했다.

EUV 라인 에지 러프니스 해결하는 새로운 식각 기술

EUV 시스템은 포토레지스트에서 라인과 공간 패턴을 선명하게 정의하는데 필요한 광자를 더 적게 생성한다. 그 결과 거친 라인 에지가 웨이퍼에 식각돼 칩에 단선, 단락 회로가 생성될 수 있다. 이 같은 수율 저하 결함은 반도체 제조사가 라인과 패턴 간 간격이 더 좁은 옹스트롬 시대에 설계를 구현하면서 더욱 빈번히 발생하고 있다.

어플라이드는 동일 챔버에서 증착과 식각을 모두 지원하는 ‘Sym3 Y 매그넘(Magnum)’ 식각 시스템을 공개했다. 독창적인 이 시스템은 거친 에지를 따라 물질을 증착해 EUV 라인 패턴을 웨이퍼 식각 전 더 매끄럽게 만들어 수율을 높이고 라인 저항을 감소시켜 칩 성능과 전력 소비를 개선한다. Sym3 Y 매그넘은 파운드리 로직에서 이미 주요 반도체 제조사의 중요한 식각 분야에 채택되고, 현재 옹스트롬 시대 노드에서 EUV 패터닝에 사용되고 있다. 메모리 분야에서 Sym3 Y 매그넘은 D램 EUV 패터닝에 가장 널리 채택된 식각 기술이다.

옹스트롬 시대 패터닝을 위한 ‘새로운 CVD 패터닝 필름’

어플라이드는 ‘프로듀서 XP 파이오니어 CVD(Producer XP Pioneer CVD)’ 패터닝 필름을 공개했다. 파이오니어 필름은 포토레지스트 패턴 공정 전 웨이퍼에 증착되며, 뛰어난 충실도로 웨이퍼에 원하는 패턴을 형성하기 위해 특별히 설계됐다. 파이오니어는 최첨단 공정 노드에 사용되는 식각 화학 물질에 대한 탄성력이 높은 고유의 고밀도 탄소 화학식을 기반으로 해 측벽 패턴 형태 균일도가 뛰어난 더욱 얇은 필름 스택을 가능하게 한다. 주요 메모리 제조사들은 이미 파이오니어를 채택해 D램 패터닝에 이용하고 있다.

파이오니어는 어플라이드의 스컬프타 패턴 형성 기술과 함께 최적화돼 패터닝 엔지니어들은 패턴을 최대로 늘리면서 기존 EUV 패턴을 엄격히 제어할 수 있다. 파이오니어는 새로운 Sym3 Y 매그넘 식각 시스템과 함께 최적화돼 로직 및 메모리 공정에 중요한 식각 분야에서 기존 탄소 필름보다 더 높은 선택비와 향상된 제어력을 제공한다.

배치 오류 방지하는 ‘아셀타’

어플라이드의 업계 선도 전자빔(eBeam) 계측 시스템은 세계 유수의 로직 및 메모리 기업이 가장 중요한 EUV 패터닝 활용 분야를 개발하고 제어하는데 이용된다. 이들의 가장 큰 과제는 각 층마다 수십억 개의 형상을 빈틈없이 정의하고 배치해 칩의 다음 층에 있는 반대 형상과 적절히 정렬시키는 것이다. 작은 배치 오류는 칩 성능과 전력 소비를 저하시키고, 오류가 크면 수율이 떨어지는 결함이 발생한다.

어플라이드는 컨투어(contour)를 이용한 설계 기반 계측 분야 기술 선도 기업 아셀타 나노그래픽스(Aselta Nanographics)를 인수했다. 컨투어를 통해 패터닝 엔지니어는 패터닝 필름과 웨어퍼에서 각 레시피가 만들어내는 형상에 대해 몇 배 더 많은 데이터를 수집할 수 있다. 이 데이터는 다시 리소그래피와 공정 흐름에 제공돼 더욱 정확한 온칩(on-chip) 기능과 배치를 생성한다.

키이스 웰스(Keith Wells) 어플라이드 머티어리얼즈 이미지 및 프로세스 제어 총괄 그룹 부사장은 “아셀타의 컨투어 기술은 현재 어플라이드의 베리티 SEM(Verity SEM) CD-SEM(패턴 거리 측정 주사전자현미경) 시스템과 프로비전(PROVision) 전자빔 계측 시스템에 통합돼 반도체 제조사에 옹스트롬 시대의 모든 계측 문제를 해결하는 고유의 엔드 투 엔드 기능을 제공한다”고 말했다.

어플라이드 패터닝 포트폴리오 및 비즈니스 성장

2012년부터 어플라이드는 패터닝을 R&D 우선순위에 두고 있다. 특히 신생 EUV 및 하이 NA EUV 활용 분야에서 고객의 가장 어려운 패터닝 문제를 해결할 수 있는 신규 제품과 솔루션 제공에 투자해왔다. 현재 어플라이드의 패터닝 제품 포트폴리오는 CVD(화학기상증착)와 ALD(원자층증착), 4종의 재료 제거(식각, 선택적 제거, 패터닝, CMP), 열 공정, 전자빔 계측 등을 포함한다. 어플라이드는 패터닝 유효 시장(SAM) 규모를 2013년 약 15억달러에서 2023년 80억달러 이상, 같은 기간 기회 점유율을 약 10%에서 30% 이상 증가시켰다.

웹사이트: http://www.appliedmaterials.com/ko

연락처

어플라이드 머티어리얼즈 코리아 홍보대행

KPR

정숙영

02-3406-2183

이메일 보내기