어플라이드 머티어리얼즈, 옹스트롬 시대 로직 칩 위한 증착 시스템 발표

새로운 칩 제조 시스템, 3D GAA 트랜지스터의 가장 미세한 원자 수준 구조 형성

Precision 선택적 질화막 PECVD 시스템, STI 무결성 유지… 기생 커패시턴스 감소 및 칩의 와트(W)당 성능 향상

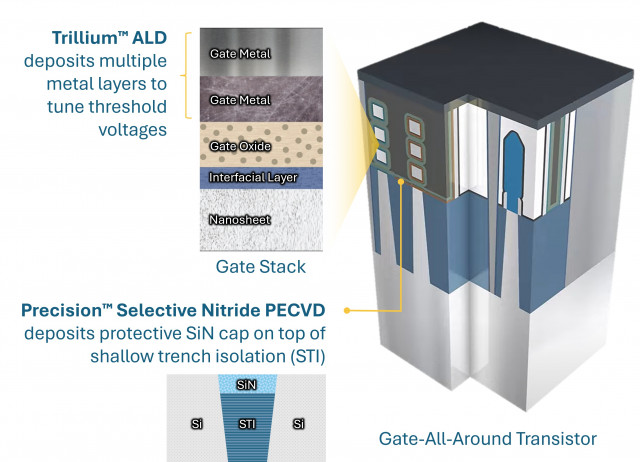

Trillium ALD 시스템, 실리콘 나노시트에 복잡한 메탈 게이트 스택 증착… 다양한 AI 컴퓨팅 애플리케이션에 최적화된 트랜지스터 구현

선도 파운드리·로직 제조사들이 현재 2나노 이하 공정에서 사용

원자 수준의 정밀도로 소재 증착을 제어하는 이 기술은 오늘날 칩 제조사가 글로벌 AI 인프라 구축 속도에 맞춰 더 빠르고 전력 효율적인 트랜지스터를 대규모로 제조할 수 있도록 지원한다.

AI 컴퓨팅 수요 급증에 따라 반도체 산업은 프로세서 칩에 집적된 수천억 개 트랜지스터에서 높은 에너지 효율 성능을 끌어내기 위해 스케일링 한계에 도전하고 있다. 이 같은 과제에 대응해 전 세계 선도적인 로직 칩 제조사들은 2나노 이하 공정에서 새로운 GAA(게이트올어라운드) 트랜지스터를 도입하고 있다.

GAA 전환은 동일 전력에서 훨씬 높은 성능을 구현하지만 성능 향상을 위한 공정 복잡도는 크게 증가한다. GAA 트랜지스터 내부의 복잡한 3D 구조를 형성하려면 500개 이상의 공정 단계가 필요하며, 이 중 상당수는 개별 원자 크기에 근접하는 허용 오차 내에서 소재를 정밀하고 반복 가능하게 제어·증착하는 새로운 방식을 요구한다.

어플라이드는 GAA 트랜지스터의 가장 복잡한 구조를 형성하기 위해 소재 혁신을 활용하는 두 가지 칩 제조 시스템을 공개했다. 새로운 기술은 첨단 칩의 성능과 전력 효율에 결정적 영향을 미치는 필수 소재인 금속과 절연 유전체의 증착을 가능하게 한다.

프라부 라자(Prabu Raja) 어플라이드 머티어리얼즈 반도체 제품 그룹(SPG) 사장은 “반도체 산업은 기존 리소그래피 기반 칩 스케일링만으로는 한계에 다다른 급격하고 비선형적 변화의 시기에 진입하고 있다”며 “옹스트롬급 첨단 로직 노드에서 성능과 전력 효율은 이제 소재 혁신에 의해 결정된다. 새로운 증착 시스템은 어플라이드의 독보적인 재료 공학 분야 리더십을 바탕으로 고객이 AI 컴퓨팅 로드맵의 근간이 되는 핵심 트랜지스터 기술 전환을 실현하도록 지원한다”고 말했다.

Precision 선택적 질화막 PECVD 시스템, STI 무결성 유지

현재 개발 중인 차세대 AI GPU는 우표 크기 면적에 3000억 개 이상의 트랜지스터를 집적할 것으로 예상된다. 적절한 절연 없이는 전자가 인접 트랜지스터로 쉽게 확산돼 트랜지스터 사이에서 발생하는 의도치 않은 전기적 간섭 ‘기생 커패시턴스(Parasitic Capacitance)’를 유발할 수 있다. 이는 신호 속도를 저하시키고 전력을 낭비하며 칩의 와트당 성능에 부정적 영향을 미친다.

첨단 트랜지스터 아키텍처에서 STI(Shallow Trench Isolation, 얕은 트렌치 절연)는 인접 트랜지스터를 전기적으로 분리하는 데 사용된다. 이 기술은 트랜지스터 사이 표면에 트렌치를 식각한 후 실리콘 산화물과 같은 절연 유전체 소재로 채워 전하를 가두고 원치 않는 누설을 방지한다. 이런 좁은 절연 트렌치는 GAA 소자에서 가장 미세한 구조 중 하나로 대량 양산 과정에서 품질 유지가 매우 어렵다. 트렌치 형성 후 칩이 여러 추가 공정 단계를 거치면서 실리콘 산화물 절연 소재가 점진적으로 손상돼 전체 칩 성능에 부정적 영향을 미칠 수 있다.

어플라이드 ‘Producer™ Precision™(프로듀서 프리시전)’ 선택적 질화막 PECVD(Plasma-Enhanced Chemical Vapor Deposition, 플라즈마 강화 화학 기상 증착) 시스템은 업계 최초의 선택적 바텀업(bottom-up) 증착 공정으로 트렌치 내 필요한 위치에만 실리콘 질화막을 형성한다. 실리콘 산화물 위에 치밀한 실리콘 질화막층을 증착해 이후 공정 단계에서 STI 소재가 리세스(recess)되는 것을 방지한다. 이 공정은 하부막이나 구조에 손상을 주지 않도록 저온에서 수행된다. Precision 선택적 질화막은 절연 트렌치의 원래 형상과 높이를 보존함으로써 일관된 전기적 특성을 유지하고 기생 커패시턴스를 감소시키며 누설을 낮추고 전체 소자 성능을 향상시킨다.

선도적인 로직 칩 제조사들이 Precision 선택적 질화막 PECVD 시스템을 현재 2나노 이하 GAA 공정 노드에서 채택하고 있다.

Trillium ALD 시스템, 원자 수준 균일도로 복잡한 메탈 게이트 구조 형성

각 GAA 트랜지스터는 트랜지스터를 켜고 끄는 데 필요한 임계 전압을 결정하는 여러 금속층으로 구성된 게이트 스택에 의해 제어되는 스위치다. 데이터센터부터 엣지에 걸쳐 AI 워크로드 요구를 충족하기 위해 칩 제조사는 설계자에게 다양한 트랜지스터 옵션을 제공한다. 그중 일부는 최고 성능을 위해 더 빠른 스위칭에 최적화되고 다른 일부는 최소 전력으로 스위칭하도록 튜닝된다. 이 같은 트레이드 오프(Trade-off)를 충족하는 것은 고정밀 금속 증착 기반의 메탈 게이트 스택 최적화에 달려 있다.

GAA 트랜지스터에서 게이트 스택은 약 10나노미터, 즉 사람 머리카락 너비의 약 1만분의 1 간격으로 배치된 여러 개 수평 나노시트를 완전히 감싸야 한다. 게이트 스택의 간극이나 불균일은 트랜지스터 스위칭 특성 변동을 유발하고 칩 성능, 전력 소모, 신뢰성, 수율에 부정적 영향을 미친다. 기존 금속 증착 방식은 극한의 요구 사항을 충족하기 어렵다.

어플라이드 ‘Endura™ Trillium™(엔듀라 트릴리움)’ ALD(Atomic Layer Deposition, 원자층 증착) 시스템은 가장 복잡한 GAA 트랜지스터 게이트 스택에 금속을 정밀하게 증착하기 위해 설계된 IMS(Integrated Materials Solution, 통합 재료 솔루션)이다. 이 시스템은 어플라이드가 첨단 트랜지스터 애플리케이션을 위해 메탈 ALD 기술 분야에서 구축해 온 오랜 전문성을 기반으로 한다. 여러 금속 증착 단계를 단일 플랫폼에 통합함으로써 Trillium은 칩 제조사가 다양한 트랜지스터의 임계 전압을 유연하게 튜닝하도록 지원한다.

Trillium은 반도체 산업 역사상 가장 성공적인 메탈 증착 시스템인 Endura(엔듀라) 플랫폼 기반으로 초고진공을 생성하고 유지한다. 진공 환경은 실리콘 나노시트 사이 극미세 공간에 여러 소재를 증착할 때 클린룸 대기 속 불순물로부터 웨이퍼를 보호하는 데 필수적이다. 옹스트롬 수준의 메탈 게이트 스택 두께 제어를 통해 Trillium ALD는 첨단 GAA 트랜지스터가 요구하는 튜닝 유연성과 신뢰성을 제공하는 동시에 트랜지스터 성능과 전력 효율, 신뢰성을 향상시킨다.

어플라이드 Trillium ALD 시스템은 여러 세대의 핀펫(FinFET) 공정 노드에서 메탈 게이트 스택 증착의 업계 표준으로 자리매김해 왔다. GAA 애플리케이션에 맞춰 고도로 최적화된 이 시스템은 더 얇은 일함수(work function) 금속과 GAA 구조의 제한된 공간에 대응하는 부피를 차지하지 않는 다이폴 소재를 구현하는 새로운 기능을 갖췄다. 선도적인 로직 칩 제조사들이 현재 2나노 이하 GAA 공정 노드에서 채택하고 있다.

Trillium ALD 및 Precision 선택적 질화막 시스템에 대한 자세한 정보는 어플라이드 머티어리얼즈 웹사이트에서 확인할 수 있다.

웹사이트: http://www.appliedmaterials.com/ko

연락처

어플라이드 머티어리얼즈 코리아

김지혜

031-724-6577

이메일 보내기

어플라이드 머티어리얼즈 코리아 홍보대행

KPR

김수빈

02-3406-2181

이메일 보내기

이 보도자료는 어플라이드 머티어리얼즈 코리아가(이) 작성해 뉴스와이어 서비스를 통해 배포한 뉴스입니다.