수볼타, 2012 국제전자소자학회에서 DDC 기술의 회로특성 개선 및 전력소모 감소에 관한 장점 발표

- 2013년 상반기 중 DDC 기술 기반 첫 제품 양산 예정

후지쯔 반도체의 65 나노미터 (nm) 저전력 공정을 이용한 이 측정결과는 수볼타의 파워슈링크(PowerShrink™) 저전력 CMOS 플랫폼을 아날로그와 디지털로직회로에 적용한 결과이다. 본 테스트 결과는 12월 10일부터 미 샌프란시스코에서 열리는 2012년 국제전자소자학회(IEDM)에서 수볼타와 후지쯔 반도체가 공동으로 기술한 논문을 통해 발표될 예정이다.

후지쯔 반도체의 부사장인 야기 하루요시(Yagi Haruyoshi) 박사는 “이번 IEDM 논문의 결과는 DDC 기술을 적용한 후지쯔 반도체 공정이 그 어떤 65nm 혹은 55nm 공정보다도 회로특성 개선 및 전력소모에 가장 최적화되었음을 입증하고 있다”며, “수볼타의 DDC 기술과 후지쯔 반도체의 저전력 공정의 결합은 모든 면에서 우리가 기대하는 그 이상의 성능을 보여 주었으며, DDC 기술을 55nm 공정에 적용한 첫 상용제품은 2013년 상반기 중 출시될 예정이다”라고 말했다.

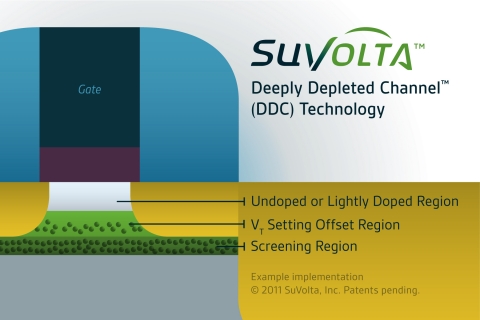

두 회사는 똑같은 회로를 두 개의 공정, 즉, 후지쯔 반도체의 표준공정과 DDC 기술을 적용한 새로운 공정으로 만들어 성능결과를 비교했다. DDC 기술의 여러 장점 중에서도, 특히 DDC 기술은 디지털 회로에서 전원전압이 1.2V 일 때 같은 전력 소모로 대략 30%의 성능개선을 할 수 있고, 전원전압이 0.9V 인 경우, 같은 성능을 보여 주면서 47%의 전력소모 감소를 이룰 수 있다. DDC 소자 특성중 전력과 성능개선에 영향을 주는 변수는 트랜지스터는 문턱전압 (VT) 의 변화폭 개선, 높은 바디계수 (body coefficient), 높은 드라이브 전류 (IEFF) 등이다.

후지쯔 반도체는 수볼타의 DDC 기술을 라이선스한 첫 번째 회사로, 두 회사는 2011년 6월에 협력관계를 발표한 이래 65nm 와 55nm 공정에서 DDC 기술을 공동 개발해 왔다. 또한, 2011년 IEDM에서 DDC기술을 후지쯔 반도체의 저전력 공정기술에 적용해 전원전압이 0.425V까지 내려가는 SRAM의 저전력 동작을 발표한 바 있다. 올해 IEDM에서 수볼타는 DDC 기술 적용 시 설계 목적에 따라 고속 혹은 저전력을 가능하게 해 주는 실리콘 결과를 발표할 예정이며, 주요 장점은 다음과 같다.

- 링 진동자 (Ring Oscillator) 회로에서 같은 진동주파수로 대략 50%의 전력소모 감소, 또는 같은 전력 소모로 30% 의 성능 개선

- 글로벌 문턱전압 (VT) 변화폭의 1-시그마 개선

- 저 전원전압 (VDD) 에서 80% 까지 높은 드라이브전류 (IEFF)

- 바디바이어싱을 통해 공정코너에 따른 변화의 축소

- 연산증폭기(OTA) 에서 낮은 전원전압으로 동작시키면서도 12dB 이득(gain) 증가

- 전류 미러 (Current Mirror) 회로에서 로컬매칭과 글로벌 매칭특성 개선

수볼타의 사장 겸 대표이사인 브루스 맥윌리엄스(Bruce McWilliams) 박사는 “DDC 기술 기반 55nm 후지쯔 반도체 공정을 이용한 제품을 곧 선보일 수 있게 되어 대단히 기쁘다”며, “수볼타의 DDC 기술이 제공하는 상당한 성능 개선 및 최대 50%의 전력 소모 감소를 통해, 수볼타는 CMOS 기술의 장점을 증대시키는 한편, 탄력적이면서도 비용효율적인 소자 기술 옵션을 업계에 제공해 나갈 것”이라고 말했다.

2012년 국제전자소자학회 (IEDM) 는 12월 10일부터 12일까지 샌프란시스코의 유니온 스퀘어에 위치한 힐튼 호텔에서 개최되며, 수볼타-후지쯔 반도체의 공동 논문 발표는 12월 11일 화요일, 14.4 세션을 통해 “A Highly Integrated 65nm SoC Process with Enhanced Power/Performance of Digital and Analog Circuits.”라는 제목으로 발표 될 예정이다. 보다 자세한 정보는 http://www.his.com/~iedm/에서 확인할 수 있다.

수볼타 개요

수볼타(Suvolta)는 성능은 유지하면서 반도체칩의 전력 소모를 크게 절감하는 반도체 기술을 개발하고 라이선스한다. 실리콘밸리에 위치하고 있는 수볼타 팀은 세계적인 엔지니어들과 과학자들로 구성되어 있으며, 반도체 업계의 발전에 기여한 오랜 기술 개발과 혁신의 역사를 자랑한다. 회사는 대표적인 벤처 캐피털 기업인 KPCB (Kleiner Perkins Caufield & Byers), 오거스트 캐피털, NEA로부터 자금을 지원받고 있다. 보다 자세한 정보는 www.suvolta.com를 방문하면 된다.

웹사이트: http://www.suvolta.com

연락처

수볼타 홍보대행

The Hoffman Agency Korea

이혜림

02-737-2942

이메일 보내기